瞬态热测试在内存模块热分析中的应用

日期:2018-12-18

▽

摘要

与传统的稳态热特性技术相比,电子瞬态测试方法具有精度高,复现性好和数据翔实等特点,所以它已经逐渐成为一种高精度热测试的标准应用。本文介绍了如何使用瞬态测试技术对一条有16个芯片的内存模块进行热分析。模块的边界条件和损耗分布是研究工作中的两个变量。通过对瞬态温度测量数据进行反卷积网络计算,我们可以识别其结构函数。比较不同的结构函数可以揭示一个芯片和多个发热芯片在热流路径上的差异。我们成功地在一个三维内存模块上使用了瞬态热测试方法,并且确定了总动态热阻的影响因素,这些因素包括了散热器,插槽和导热界面材料。传统的稳态热分析技术很难获得关于三维元件这方面的信息。热设计工程师可以通过这些信息去区分散热设计中材料的优点和热交换的机理,从而降低整个散热设计的成本。

▽

介绍

内存模块的热损耗不断增加,这就需要更高效地散热设计。提高内存模块的散热效率,就需要我们了解模块中每一部分的传热路径,热阻和热容。传统的热稳态和JEDEC标准测试方法使用的是一维热流的方法,提供的也仅仅是一个总的热阻值。此外,对于表面具有散热器的内存元件,很难在不同的位置布置热电偶和实时监控其温度变化。因此,我们提出了一个基于电子瞬态方法的内存热分析方法。

第一个提出电子瞬态方法测量元件结温是70 年代的Blackburn等人。之后Siegel提出了一种从电子瞬态测量数据中提取2个或3个主要热流时间常数的方法。再往后,Sofia提出了一种使用电子瞬态测试方法从塑料封装中区分陶瓷封装的方法。1988年,Szbkely提出了一种通过反卷积识别网络的详细方法,这种方法提供了精确的数学方法以获得完整的各部分时间常数,动态热阻和热容。通过这些年的研究,在热测试方面的电子瞬态测试方法取得了很大地进展。

在测试中使用半导体元件作为温度传感器有以下优点:

1. 与热电偶相比二极管,晶体管和MOSEFT 等半导体元件具有更高的温度敏感性。常见的半导体元件温度敏感性大约是mV/oC,而热电偶是μV/oC。

2. 半导体元件对于温度变化有着更快地动态响应。

3. 半导体温度传感器具有很好的复现性和不受人为因素影响的优点。

4. 不需要像热电偶一样插入式布置。像表面有散热器的内存模块等这类非常紧凑的器件很难布置插入式的温度传感器。

5. 直接获得被测试元件的结温要比通过壳温推算得到的结温要更精确。

在测试中使用半导体元件作为温度传感器有以下优点:

1. 与热电偶相比二极管,晶体管和MOSEFT 等半导体元件具有更高的温度敏感性。常见的半导体元件温度敏感性大约是mV/oC,而热电偶是μV/oC。

2. 半导体元件对于温度变化有着更快地动态响应。

3. 半导体温度传感器具有很好的复现性和不受人为因素影响的优点。

4. 不需要像热电偶一样插入式布置。像表面有散热器的内存模块等这类非常紧凑的器件很难布置插入式的温度传感器。

5. 直接获得被测试元件的结温要比通过壳温推算得到的结温要更精确。

除了以上的优点之外,通过电子瞬态测试方法记录的温度随时间变化的曲线可以得到每一部分的瞬态热阻,热容和时间常数等信息。然而,精确的卷积处理需要一个非常好的数据识别系统,高信噪比和快速响应时间。对于精确的瞬态测试而言,这些都是非常重要的。测量结果和之后计算得到数据的精度使电子瞬态测试技术对于三维复杂散热系统有很大的吸引力。

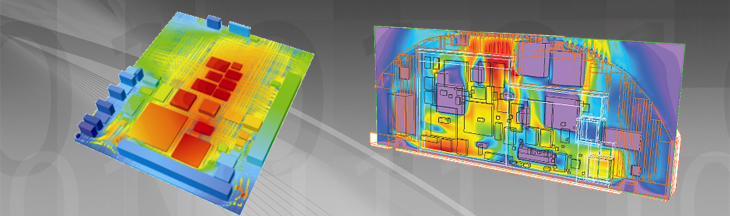

在本文的研究中,用于测试的内存模块总共有16 个芯片,每一侧8个芯片。每一个芯片中都被嵌入了一个38欧姆的加热器,以模拟内存工作期间产生的热量。此外,这个38欧姆的加热器也作为温度传感器。当传感器电流为25mA时,这个传感器的敏感度为3.792mV/oC,这个传感器使用一个温度范围为20~80oC 的热电恒温调节器进行校准。模块的结构图如下:

.jpg)

图 1 .内存模块结构图

▽

测量

在测试期间,内存被放置在一个自然对流的恒温箱内,并且对一个或多个芯片施加了一个持续1800S的热功耗。之后,停止施加热功耗,并且监控之后1800S的温度变化。在热功耗停止施加后的1微秒后,开始连续记录温度变化。仅仅对一个芯片(芯片0)应用了1.6W的热功耗。从图2中我们可以看到被加热的芯片温度在停止施加热功耗后的0.1ms内发生了变化。由于与被加热芯片的热交换,其它芯片的温度至少在1s中之后变化。最后所有的芯片都达到同一个稳定的温度。由于自然对流空间具有很大的热容,所以测试通常需要经历3600s才能达到稳定。相比之下,如果边界条件为冷板,测试的时间会大为缩短,大约为30~60s。尽管测试时间比较长,但瞬态测试方法可以确定芯片结点至环境空气的动态热阻,对于其它的热边界条件而言,自然对流环境是最恶劣的边界条件,并且经常被用于参考。

.jpg)

图 2 .在芯片0 停止施加热功耗后,内存一侧8 个芯片的温度变化

使用反卷积网络计算可以从温度变化曲线中,得到热阻抗,复合位点,热阻和时间常数和结构函数。结构函数是热流路径独一无二的描述。它是沿着热流流动路径上每一部分动态热阻和热容关系的图线。

图 3 .内存模块中各部分对于结构函数的影响

▽

结果和讨论

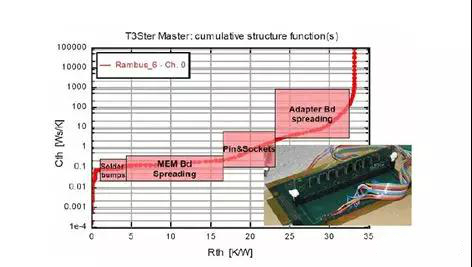

首先我们研究有散热器和没有散热器两种情况下,结点至环境空气的热阻(Ɵja)。16 个芯片中只有一个被加热。除了结构函数中描述芯片层的第一部分之外,两个方案中的其它部分曲线有很大差异。在具有散热器和导热界面材料的方案中,在芯片层之后热容有很大的增加。图4中以蓝色曲线显示。没有散热器的方案中,热量主要通过导热的方式进入插槽,之后再经过PCB板,最后进入到空气中。两条不同的散热路径有不同的总热阻Ɵja。最大的热阻差23K/W是由于散热器所引起的,散热器可以使发热芯片的局部动态热阻更低。热量通过散热器传递到不发热的芯片上。下图是芯片0被施加热功耗之后,有散热器和没有散热器两种情况的结构函数。

图 4 .两种情况的结构函数

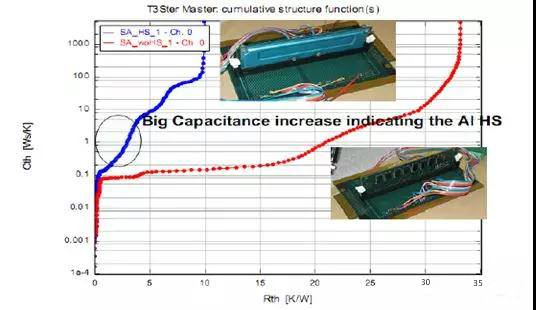

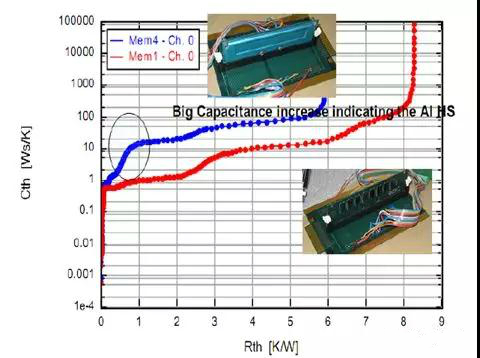

之后的测试中使用同样的方法,只是同一时间对内存模块一侧的八个芯片同时进行加热。图5显示了两种情况的结构函数曲线几乎平行,只是在有铝散热器的情况中热阻有一个突增。具有散热器的Ɵja是6K/W,而没有散热器的Ɵja是8.3K/W。当内存一侧八个芯片同时被施加一样的热损耗,散热器的温度梯度非常小。Ɵja 差变小的原因是由于散热器的表面积比八个芯片的总表面积要大。这个结果表明散热器不能减少同时发热芯片的局部动态热阻。我们可以得出如下结论,当仅仅一个芯片散发热量,散热器会将热量进行横向传递,从而大幅度的减少了加热芯片结点和环境空气之间的总热阻。下图显示8个芯片同时被加热时,有和没有散热器的内存结构函数对比。

图 5 .有和没有散热器的结构函数对比

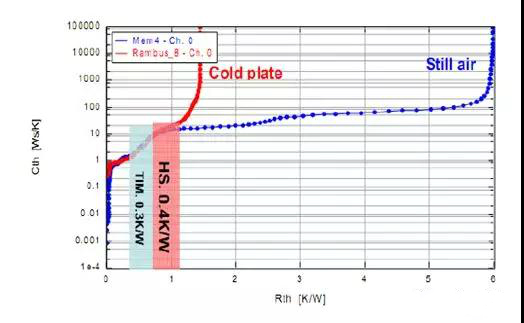

当一个芯片发热时,散热器的热扩散影响在热流从发热芯片到TIM材料中占主导地位。所以,类似TIM这类材料详细的结构很难从结构函数中识别,除非我们对测试方法做一些改进。为了得到一个精确的TIM热容和动态热阻估计,我们采用冷板作为边界条件,从而增加TIM两侧的温度梯度。通过在内存模块一侧贴上冷板,另一面贴上Teflon绝缘纸。当所有的八个芯片同时发热,在冷板和发热芯片之间出现了一条几乎没有热扩散的散热路径。通过这种方式,我们可以提高结构函数的分辨率,从而可以清楚地识别TIM材料。在测试期间,在内存靠近冷板一侧的八个芯片总共散发了3.27W的热量。从芯片结点到TIM,散热器和最终的冷板之间几乎形成了一条一维的散热路径。图6中显示了从测试数据中获得的芯片结点和空气之间的结构函数。我们可以从结构函数中,方便地确定出TIM和散热器的动态热阻值分别为0.3和0.4K/W。下图是当内存一侧8个芯片同时被加热时,冷板和自然对流两种不同边界条件下的结构函数对比。

图 6 . 两种不同边界条件下的结构函数对比

图6 中蓝线显示的是自然对流环境中没有冷板的结构函数。TIM材料的热阻在总的结点至环境6K/W的热阻值中占了很小一部分。即便TIM的热阻值可以被进一步地减小到目前0.3K/W以下,但它不会影响总的热阻值。

结果

在本文中,我们讨论了电子瞬态测试方法在分析内存三维热阻方面的优点。我们研究了不同热损耗情况下,不同损耗分布和边界条件下的传热路径,动态热阻和热容。通过比较由不同边界条件测试数据所提取的结构函数,我们可以了解芯片结点到环境之间每一部分对总热阻的影响。瞬态分析技术证实了当内存的一个芯片发热时,散热器会将热量向侧面传递,从而减少了总的热阻值。当同一时间内内存的多个芯片发热时,TIM和散热器仅仅占到总热阻中很少的一部分,因此TIM材料的散热性能提升不会对整个散热设计带来太多的好处。本文没有提及,但在参考文献9和10中提到了在不同工作周期下每一部分的热阻抗,热时间常数和脉冲热阻值。这些信息也可以通过对本文获得的瞬态测试数据做进一步处理得到。

▽

参考

1. Heejin Lee, Haehyung Lee, Joonghyun Baek, Taegyeong Chungand Seyong Oh, “Thermal

Management of High Power Memory Module”, Proceedings of 22ndIEEE SEMI-THERM

Symposium, Dallas, Tx, Mar. 14-16th , 2006

2. 2. Mohammad M Hossain, Yongje Lee, Roksana Akhter, DerejeAgonafer, Senol Pekin

and Terry Dishongh, “Reliability of Stack Packaging Varyingthe Die Stacking Architectures

for Flash Memory Applications” Proceedings of 22nd IEEESEMI-THERM Symposium,

Dallas, Tx, Mar. 14-16th, 2006

3. JESD 51-1, http://www.jedec.org

4. Blackburn, D.L., Oettinger, F.F., "Transient ThermalResponse Measurements of Power

Transistors," IEEE Power Electronics SpecialistsConference (PESC), 1974 Record, June

1974, pp 140-148

5. B. S. Siegel, Electronics 51, 121 (1978).

6. Sofia, J.W., "Analysis of Thermal Transient Datawith Synthesized Dynamic Models for

Semiconductor Devices", IEEE Transactions onComponents, Packaging, and Manufacturing

Technology Part A (CPMT), Volume 18, March 1995, pp 39-47

7. V.Szekely, “A new evaluation method of thermal transientmeasurement results”,

Microelectronics Journal 28 (1997) 277-292

8. V.Székely, Tran Van Bien: “Fine structure of heat flowpath in semiconductor devices: a

measurement and identification method”, Solid-StateElectronics, V.31, No.9, pp.1363-1368

(1988)

9. Oliver Steffens, Péter Szabó1, Michael Lenz, GáborFarkas, “Thermal transient

characterization methodology for single-chip and stackedstructures” Proceedings of 21st

IEEE SEMI-THERM Symposium, San Jose, CA, Mar. 10-12th, 2005

10. G. Farkas, A. Poppe, E. Kollar, P. Stehouwer, “Dynamiccompact models of cooling mounts

for fast board level design”, Proceedings of 19th IEEESEMI-THERM Symposium, San

Jose, CA, Mar. 11-13th, 2003

▽

沪公网安备 31010602003953号

沪公网安备 31010602003953号